数字电子钟逻辑电路设计报告(DOC 22页)

数字电子钟逻辑电路设计报告(DOC 22页)内容简介

、前言1

三、单元模块设计6

三、单元模块设计

二、总体方案设计4

二、总体方案设计

五、设计总结

五、设计总结15

1.各单元模块功能介绍及电路设计6

1.电气性能相互匹配问题

1.设计的小结15

1.1秒脉冲发生器

1.2秒、分为00―59六十进制计数器

1.3星期、日为七进制计数器和24进制计数

1.4校正电路

1.5整点报时电路

1.各单元模块功能介绍及电路设计

1.方案比较

1.方案比较4

1.设计的小结

1.设计目的

1.设计目的1

1、方案一

1、调试示波器,时钟模块是否能产生1Hz的矩形波。

1.CD4511、74HC00H、74HC04H、74HC161及数码管

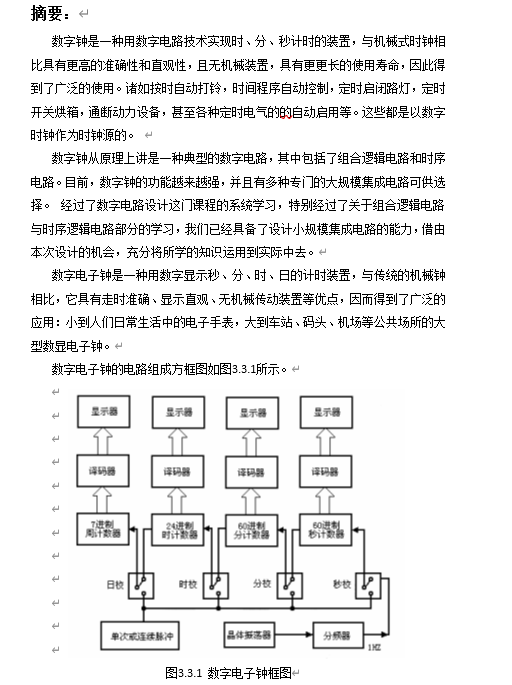

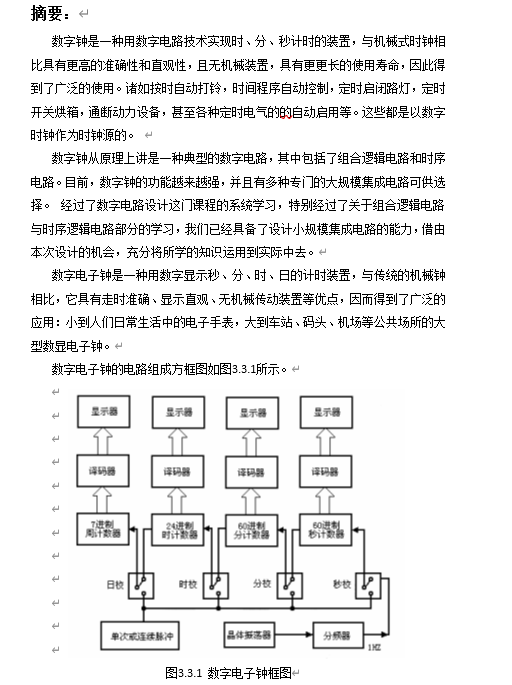

1.由晶振电路产生1Hz标准秒信号。

1.秒脉冲发生器

2.方案论证:5

2.电路参数的计算及元器件的选择10

2.指标要求

2.指标要求1

2.方案论证:

2.时序配合

2.电路参数的计算及元器件的选择

2.设计收获体会

2.设计收获体会16

2、调试电子钟,察看是否能够正常运行。

2.晶振32768Hz

2.秒、分为00―59六十进制计数器。

2.计数译码显示

3.对设计的进一步完善提出意见或建议17

3.对设计的进一步完善提出意见或建议

3.方案选择:

3.方案选择:5

3.特殊器件的介绍

3.特殊器件的介绍10

3.设计说明与思路提示

3.设计说明与思路提示1

32768Hz,通过15次二分频后可获得

1Hz的脉冲输出,电路图如图3.3.2所示。

3、观察校准电路是否正常使用。

3.时为00―23二十四进制计数器。

3.校正电路

..............................

三、单元模块设计6

三、单元模块设计

二、总体方案设计4

二、总体方案设计

五、设计总结

五、设计总结15

1.各单元模块功能介绍及电路设计6

1.电气性能相互匹配问题

1.设计的小结15

1.1秒脉冲发生器

1.2秒、分为00―59六十进制计数器

1.3星期、日为七进制计数器和24进制计数

1.4校正电路

1.5整点报时电路

1.各单元模块功能介绍及电路设计

1.方案比较

1.方案比较4

1.设计的小结

1.设计目的

1.设计目的1

1、方案一

1、调试示波器,时钟模块是否能产生1Hz的矩形波。

1.CD4511、74HC00H、74HC04H、74HC161及数码管

1.由晶振电路产生1Hz标准秒信号。

1.秒脉冲发生器

2.方案论证:5

2.电路参数的计算及元器件的选择10

2.指标要求

2.指标要求1

2.方案论证:

2.时序配合

2.电路参数的计算及元器件的选择

2.设计收获体会

2.设计收获体会16

2、调试电子钟,察看是否能够正常运行。

2.晶振32768Hz

2.秒、分为00―59六十进制计数器。

2.计数译码显示

3.对设计的进一步完善提出意见或建议17

3.对设计的进一步完善提出意见或建议

3.方案选择:

3.方案选择:5

3.特殊器件的介绍

3.特殊器件的介绍10

3.设计说明与思路提示

3.设计说明与思路提示1

32768Hz,通过15次二分频后可获得

1Hz的脉冲输出,电路图如图3.3.2所示。

3、观察校准电路是否正常使用。

3.时为00―23二十四进制计数器。

3.校正电路

..............................

下一篇:尚无数据

用户登陆

电子行业企业管理热门资料

电子行业企业管理相关下载