ПЩБрГЬТпМЦїМўЩшМЦМАгІгУЪЕбщБЈИц(DOC 33вГ)

- ЫљЪєЗжРрЃК

- PLDПЩБрГЬТпМЦїМў

- ЮФМўДѓаЁЃК

- 3324 KB

- ЯТдиЕижЗЃК

- ЯрЙизЪСЯЃК

- ПЩБрГЬ,ЩшМЦМАгІгУ,ЪЕбщБЈИц

ПЩБрГЬТпМЦїМўЩшМЦМАгІгУЪЕбщБЈИц(DOC 33вГ)ФкШнМђНщ

вЛЁЂ ЪЕбщФкШн

вЛЁЂЪЕбщФкШн

вЛЮЛШЋМгЦїЙІФмЗТецНсЙћЃК

Ш§ ЪЕбщНсЙћЬжТлЗжЮі

ДЎааЭЈаХ:Ъ§ОнвЛЮЛвЛЮЛДЮађЗЂЫЭЛђНгЪеЁЃ

Жў ЪЕбщНсЙћ

ЗТецВЈаЮЩшжУШчЯТЃК

ЗТецВтЪдЪфШыВЈаЮШчЯТЃК

ЗТецНсЙћШчЯТЃК

ПЩБрГЬТпМЦїМўЩшМЦМАгІгУ

ЙњМЪЩЯЙцЖЈЕФвЛИіБъзМВЈЬиТЪЯЕСа:

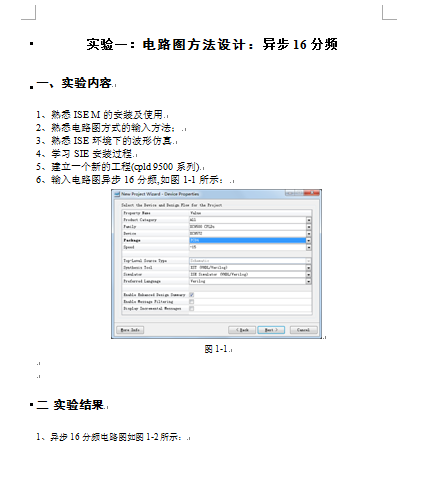

ЭМ1-1

ЭМ1-2

ЭМ1-3

ЭМ1-4

ЭМ1-5

ЭМ2-1вЛЮЛШЋМгЦї

ЭМ2-2ВЈаЮЗТецМЄРј

ЭМ2-3ФЃПщНЈСЂ

ЭМ2-4 8ЮЛШЋМгЦї(ЖЅВуЕчТЗЭМ)

ЭМ2-5 8ЮЛШЋМгЦїВЈаЮЗТецМЄРј

ЭМ2-6 ЙІФмЗТецНсЙћ

ЭМ2-7 ЙІФмЗТецНсЙћ

ЭМ2-8 ЙІФмЗТецНсЙћ

ЭМ3-1 НЈСЂвЛИіаТЕФverilogФЃПщ

ЭМ3-2 ЪфШыШЋМгЦї

ЭМ3-3 ВтЪдВЈаЮ

ЭМ3-4 ВтЪдВЈаЮ

ЭМ3-5 ЗТецВтЪдНсЙћ

ЭМ3-6 ЗТецВтЪдНсЙћ

ЭМ3-7 ЗТецВтЪдНсЙћ

ЭМ3-8 ЗТецВтЪдНсЙћ

ЭМ4-1 LEDЯдЪОФЃПщ

ЭМ4-2 Ъ§ОнЫјДцФЃПщ

ЭМ4-3 ЖЅВу

ЭМ4-4 ВтЪдВЈаЮ

ЭМ4-5 ЗТецНсЙћ

ЭМ4-6 ВтЪдВЈаЮ

ЭМ4-7 ЗТецНсЙћ

ЭМ5-1 ФЃЪНПижЦФЃПщ

ЭМ5-10 ЗТецНсЙћ

ЭМ5-11 ВтЪдВЈаЮЩшжУ

ЭМ5-12 ЗТецНсЙћ

ЭМ5-13 ВтЪдВЈаЮЩшжУ

ЭМ5-14 ЗТецНсЙћ

ЭМ5-15 ВтЪдВЈаЮЩшжУ

ЭМ5-16 ЗТецНсЙћ

ЭМ5-17 ЗТецНсЙћ

ЭМ5-18 ЖЅВуЮФМў

ЭМ5-19 ВтЪдВЈаЮ

ЭМ5-2 ВЈЬиТЪЗЂЩњФЃПщ

ЭМ5-20 ВтЪдВЈаЮ

ЭМ5-21 ЗТецНсЙћ

ЭМ5-22 ЗТецНсЙћ

ЭМ5-3 ЗЂЫЭЪ§ОнФЃПщ

ЭМ5-4 ЗЂЫЭЪ§ОнФЃПщ

ЭМ5-5 ВтЪдВЈаЮЩшжУ

ЭМ5-6 ЗТецНсЙћ

ЭМ5-7 ВтЪдВЈаЮЩшжУ

ЭМ5-8 ЗТецНсЙћ

ЭМ5-9 ВтЪдВЈаЮЩшжУ

..............................

вЛЁЂЪЕбщФкШн

вЛЮЛШЋМгЦїЙІФмЗТецНсЙћЃК

Ш§ ЪЕбщНсЙћЬжТлЗжЮі

ДЎааЭЈаХ:Ъ§ОнвЛЮЛвЛЮЛДЮађЗЂЫЭЛђНгЪеЁЃ

Жў ЪЕбщНсЙћ

ЗТецВЈаЮЩшжУШчЯТЃК

ЗТецВтЪдЪфШыВЈаЮШчЯТЃК

ЗТецНсЙћШчЯТЃК

ПЩБрГЬТпМЦїМўЩшМЦМАгІгУ

ЙњМЪЩЯЙцЖЈЕФвЛИіБъзМВЈЬиТЪЯЕСа:

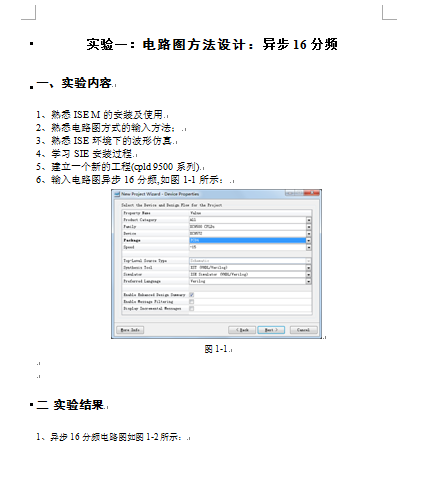

ЭМ1-1

ЭМ1-2

ЭМ1-3

ЭМ1-4

ЭМ1-5

ЭМ2-1вЛЮЛШЋМгЦї

ЭМ2-2ВЈаЮЗТецМЄРј

ЭМ2-3ФЃПщНЈСЂ

ЭМ2-4 8ЮЛШЋМгЦї(ЖЅВуЕчТЗЭМ)

ЭМ2-5 8ЮЛШЋМгЦїВЈаЮЗТецМЄРј

ЭМ2-6 ЙІФмЗТецНсЙћ

ЭМ2-7 ЙІФмЗТецНсЙћ

ЭМ2-8 ЙІФмЗТецНсЙћ

ЭМ3-1 НЈСЂвЛИіаТЕФverilogФЃПщ

ЭМ3-2 ЪфШыШЋМгЦї

ЭМ3-3 ВтЪдВЈаЮ

ЭМ3-4 ВтЪдВЈаЮ

ЭМ3-5 ЗТецВтЪдНсЙћ

ЭМ3-6 ЗТецВтЪдНсЙћ

ЭМ3-7 ЗТецВтЪдНсЙћ

ЭМ3-8 ЗТецВтЪдНсЙћ

ЭМ4-1 LEDЯдЪОФЃПщ

ЭМ4-2 Ъ§ОнЫјДцФЃПщ

ЭМ4-3 ЖЅВу

ЭМ4-4 ВтЪдВЈаЮ

ЭМ4-5 ЗТецНсЙћ

ЭМ4-6 ВтЪдВЈаЮ

ЭМ4-7 ЗТецНсЙћ

ЭМ5-1 ФЃЪНПижЦФЃПщ

ЭМ5-10 ЗТецНсЙћ

ЭМ5-11 ВтЪдВЈаЮЩшжУ

ЭМ5-12 ЗТецНсЙћ

ЭМ5-13 ВтЪдВЈаЮЩшжУ

ЭМ5-14 ЗТецНсЙћ

ЭМ5-15 ВтЪдВЈаЮЩшжУ

ЭМ5-16 ЗТецНсЙћ

ЭМ5-17 ЗТецНсЙћ

ЭМ5-18 ЖЅВуЮФМў

ЭМ5-19 ВтЪдВЈаЮ

ЭМ5-2 ВЈЬиТЪЗЂЩњФЃПщ

ЭМ5-20 ВтЪдВЈаЮ

ЭМ5-21 ЗТецНсЙћ

ЭМ5-22 ЗТецНсЙћ

ЭМ5-3 ЗЂЫЭЪ§ОнФЃПщ

ЭМ5-4 ЗЂЫЭЪ§ОнФЃПщ

ЭМ5-5 ВтЪдВЈаЮЩшжУ

ЭМ5-6 ЗТецНсЙћ

ЭМ5-7 ВтЪдВЈаЮЩшжУ

ЭМ5-8 ЗТецНсЙћ

ЭМ5-9 ВтЪдВЈаЮЩшжУ

..............................

ЩЯвЛЦЊЃКХфСЯЛњpldЪЙгУЫЕУїЪщЃЈDOC 48вГЃЉ

гУЛЇЕЧТН

PLDПЩБрГЬТпМЦїМўШШУХзЪСЯ

PLDПЩБрГЬТпМЦїМўЯрЙиЯТди

- NIOSВЮгыcycАцдРэЭМ(pdf 9вГ)

- ЕчТЗЕФЗжЮігыжЊЪЖвЊЕу(ppt 66вГ

- ALTERA аТвЛДњCPLDМђНщ

- FPGAгІгУЯъНщ(doc 49вГ)

- PLDЩшМЦЮЪД№НтЮі(doc 22вГ)

- ВЩгУVHDLНјааИпВуДЮЩшМЦ.

- ПЩБрГЬТпМЦїМўPLDХрбЕНЬВФ(PP

- MaxplusIIМђвзгУЛЇЪЙгУШыУХжИФЯ

- ЕчЦјПижЦгыPLC(вЛ)(ppt 79вГ)

- CWIХрбЕзЪСЯжЎКИНгЙЄвебЇ(pdf

- МИжжFPGAЕФFIRТЫВЈЦїЗНАИЯъЮі(

- PLCЫЋЛњШШБИММЪѕЕФжївЊЬиЕугыгІ

- quartus IIжаЮФгУЛЇНЬГЬ(pdf 5

- МЏГЩЕчТЗГЃгУЕЅДЪ(doc 20вГ)

- ЕчЦјПижЦгыPLC(Жў)(ppt 88вГ)